Cortex-M3¶

简介¶

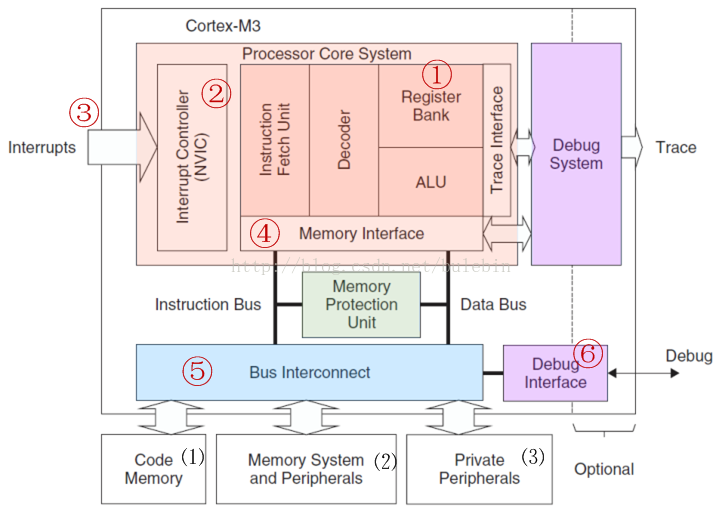

Cortex-M3 是一个 32 位处理器内核,内部的数据路径是 32 位,寄存器是 32 位,存储器接口是 32 位。

采用了哈佛结构,三级流水线,但增加了分支预测功能,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。这样一来数据访问不再占用指令总线,从而提升了性能。

Cortex-M3采用了Tail-Chaining中断技术,完全基于硬件进行中断处理,最多可减少12个时钟周期数,在实际应用中可减少70%中断。

指令集¶

Cortex-M3 只使用 Thumb-2 指令集,它允许 32 位指令和 16 位指令水乳交融,代码密度和处理性能两手抓。

只使用Thumb-2 指令集比传统ARM处理器优势: * 1、消灭了状态切换的额外开销,节省了执行时间和指令空间。 * 2、不需要把源代码分成ARM编译和Thumb编译,软件开发的管理大大减少。 * 3、无需再反复求证和测试:究竟在何时何地切换到何种状态,程序才最有效率。

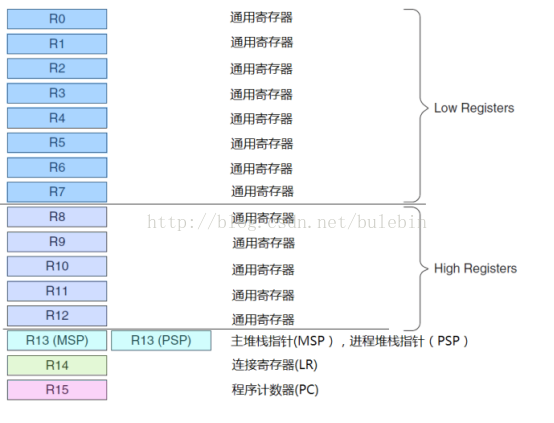

寄存器¶

中断优先级¶

分为抢占式优先级和响应优先级,每个中断源都需要被指定这两种优先级。

1、抢占优先级不同,会涉及到中断嵌套,抢占优先级高的会优先抢占优先级低的,优先得到执行。(注意:优先级数字越小,优先级越高)

2、抢占优先级相同,不涉及到中断嵌套,响应优先级不同,响应优先级高的先响应。(例如:两个中断同时响应,这里就会先执行响应优先级高的那个中断)(注意:优先级数字越小,优先级越高)

3、抢占优先级和响应优先级都相同,则比较它们的硬件中断编号,中断编号越小,优先级越高。(硬件中断编号从中断向量表当中查看)

优先级使用寄存器使用四位,分别用于定义抢占优先级及相应优先级

ARM处理器7种工作模式(特权模式,异常模式):

用户模式(USR):正常程序执行模式,不能直接切换到其他模式

系统模式(SYS):运行操作系统的特权任务,与用户模式类似,但具有可以直接切换到其他模式等特权

快中断模式(FIQ):支持高速数据传输及通道处理,FIQ异常响应时进入此模式

中断模式(IRQ):用于通用中断处理,IRQ异常响应时进入此模式

管理模式(SVC):操作系统保护模式,系统复位和软件中断响应时进入此模式(由系统调用执行软中断SWI命令触发)

中止模式(ABT):用于支持虚拟内存和/或存储器保护,在ARM7TDMI没有大用处

未定义模式(UND):支持硬件协处理器的软件仿真,未定义指令异常响应时进入此模式

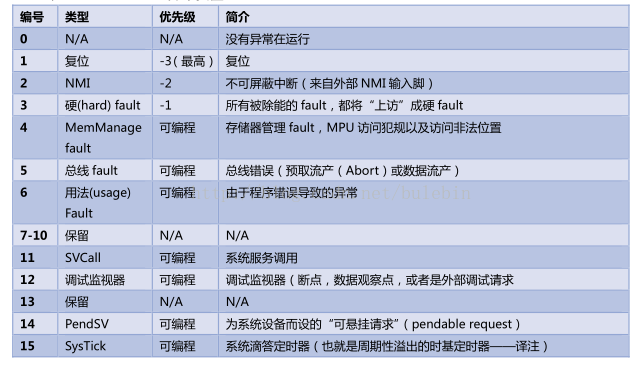

中断和异常¶

Cortex-M3 的所有中断机制都由 NVIC 实现。除了支持 240 条中断之外, NVIC 还支持 16-4-1=11 个内部异常源(4+1个为保留),可以实现 fault 管理机制。结果, Cortex-M3 有了 256 个预定义的异常类型。

虽然 Cortex-M3 支持 240 个外中断,但具体使用了多少个是由芯片生产商决定。 Cortex-M3 还有一个 NMI (不可屏蔽中断)输入脚,当它被置为有效时, NMI 服务函数会无条件地执行。

NVIC¶

嵌套向量中断控制器NVIC

1、可嵌套中断支持。可嵌套中断支持,覆盖所有的外部中断和绝大多数系统异常。这些异常可以赋予不同的优先级。当前优先级被存储在 xPSR 的专用字段。当一个异常发生时,硬件会字段比较该异常是否与当前的异常优先级更高,如果发现来了更高优先级的异常,处理器就会中断当前的中断服务程序,而服务新来的异常。

2、向量中断支持。当开始响应一个中断后, Cortex-M3 会自动定位一张向量表,并且根据中断号从表中找出 ISR 的入口地址,然后跳转过去执行。

3、动态优先级调整。软件可以在运行时期更改中断的优先级,如果在某 ISR 中修改了自己所对应中断的优先级,而且这个中断又有新的实例处于悬起中,也不会自己打断自己,从而没有重入风险。

4、中断延迟大大缩短。 Cortex-M3为了缩短中断延迟,引入了几个新特性,包括自动的现场保护和恢复,以及其它的措施,用于缩短中断嵌套时的ISR间延迟。

5、中断可屏蔽。既可以屏蔽优先级低于某个阈值的中断 / 异常(设置 BASEPRI 寄存器),也可以全体封杀(设置 PRIMASK 和 FAULTMASK 寄存器)。这是为了让时间关键的任务能在死线到来前完成,而不被干扰。